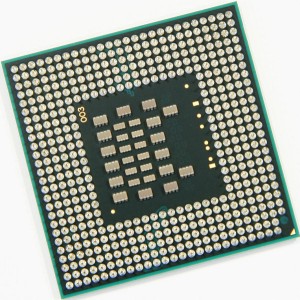

Core

Duo close up

If you've been hanging around here for a while, you may

have heard us referring to Core Duo by its code name,

Yonah, long before Intel decided to give it a somewhat

confusing official name. We previewed Yonah after last

fall's Intel Developer Forum, explaining some of the features

that make it unique. Like other dual-core processors such

as the Pentium D and the Athlon 64 X2, the Core Duo joins

together a pair of CPU cores on a single chip. In the

case of the Core Duo, those CPU cores are massaged and

tweaked versions of the Pentium M processor, familiar

as part of Intel's Centrino mobile platform. (The Pentium

M itself traces its heritage back through many earlier

Pentiums, including the Pentium III and Pentium Pro; we've

covered the Pentium M at some length in the past.)

Unlike the Pentium D, however, the Core

Duo benefits from a very intentional dual-core design.

In fact, the Core Duo's two cores are arguably more

tightly integrated than those in AMD's dual-core Athlon

and Opteron processors. Each of the Duo's cores has

a 32KB L1 cache for data and another of the same size

for instructions, but the cores share a common 2MB L2

cache via an internal, on-chip bus. Space in the L2

cache is allocated dynamically, so either core can allocate

up to the full 2MB of cache for itself, should the other

one not need it. The two cores can effectively share

the data in the L2 cache, as well. This use of a single,

unified L2 cache greatly simplifies the management of

cache coherency, especially in a single-socket system

like a laptop or desktop PC. With the Pentium D, by

contrast, cache coherency updates must constantly be

passed across the system's front-side bus, even in a

single-socket system.

Core Duo is more than just a pair of

Pentium Ms made to share a cache, though. Intel's Israel-based

CPU design team has modified the Pentium M design in

order to address some of its performance shortcomings,

especially in terms of multimedia performance. Simply

going from a single core to two will inevitably help

speed up tasks like video encoding, where the software

is typically multithreaded. But Yonah also supports

the group of 13 new instructions known as SSE3, handles

some SSE2 instructing like Shuffle and Unpack up to

30% faster, and is capable of using its instruction-grouping

abilities (known as micro-ops fusion) on some SSE instructions,

improving overall throughput. These and other enhancements

should help alleviate some of the Pentium M's few performance

weaknesses compared to today's desktop processors.

Of

course, none of these enhancements would matter much

if Intel couldn't fit the Core Duo into laptops with

about the same size, weight, battery power, and cooling

capabilities as the Pentium M. In order to make that

happen, Intel has arrayed a number of technologies in

Core Duo's favor, not least of which is its 65-nanometer

chip fabrication process. The process shrink means Core

Duo's 151 million transistors can reside in an area

only 90 mm2—barely any larger than the single-core

Pentium M "Dothan" at 84 mm2 when manufactured

with Intel's 90-nano process. The Core Duo also benefits

from the fortuitous effects of multi-core processor

designs on power consumption; by keeping clock frequencies

relatively low and doubling up on CPU logic, a dual-core

CPU can generally achieve better performance per watt

than a single-core CPU, provided that multithreaded

software is reasonably abundant. Of

course, none of these enhancements would matter much

if Intel couldn't fit the Core Duo into laptops with

about the same size, weight, battery power, and cooling

capabilities as the Pentium M. In order to make that

happen, Intel has arrayed a number of technologies in

Core Duo's favor, not least of which is its 65-nanometer

chip fabrication process. The process shrink means Core

Duo's 151 million transistors can reside in an area

only 90 mm2—barely any larger than the single-core

Pentium M "Dothan" at 84 mm2 when manufactured

with Intel's 90-nano process. The Core Duo also benefits

from the fortuitous effects of multi-core processor

designs on power consumption; by keeping clock frequencies

relatively low and doubling up on CPU logic, a dual-core

CPU can generally achieve better performance per watt

than a single-core CPU, provided that multithreaded

software is reasonably abundant.

The

Core Duo T2600 processor

These

moves to 65nm and dual cores are big steps in the fight

to keep power consumption in check, but Intel didn't

stop there. They've also given the Core Duo a range

of power management techniques that can reduce power

use when part or all of the processor is idle. The two

cores can independently manage some of their own traditional

low-power states or C-states, such as Halt, Stop-Clock,

and Sleep, so that one core could enter a lower power

mode while the other cranks away on a thread. More innovatively,

the Core Duo can choose to deactivate portions of its

shared L2 cache in stages if the current applications

don't require full use of the cache. Unneeded parts

of the cache are flushed to memory and temporarily shut

down. Should the CPU become so idle that the entire

L2 cache can be flushed to RAM, the Core Duo will enter

what Intel calls an Enhanced Deeper Sleep mode. In this

state, without the need to power the L2 cache, the processor

can operate at even lower voltages. Such C-state transitions

happen in fractions of a second, so entering or recovering

from a low-power state should be largely imperceptible

to the end user. Core Duo also carries over Intel's

Enhanced SpeedStep dynamic clock speed and voltage scaling

feature, of course, and it adds new thermal sensors

on each CPU core near likely hotspots on the chip.

Thanks

to all of these changes, Intel rates the TDP, or thermal

design power, of the first wave of Core Duo chips—ranging

from 1.66GHz to 2.166GHz—at only 31W. (TDP is

a design target for cooling solutions and doesn't necessarily

represent the peak power draw of the part.) That's up

only slightly from the 27W TDP of the faster variants

of the Dothan, like the Pentium M 770 at 2.13GHz. Intel

makes a single-core variant of Yonah called the Core

Solo, and its TDP is 27W. There are also low-voltage

versions of Core Duo with TDPs as low as 15W. All in

all, that's a mighty impressive achievement for a processor

with this sort of performance.

The

Core Duo is packed to the hilt with the latest features,

including SSE3, support for the Execute Disable Bit

for better antivirus protection, and Intel's new VT

virtualization technology. The one omission from this

list of CPU enhancements is a notable one, though: Core

Duo lacks support for EM64T, Intel's version of the

64-bit extensions to the x86 instruction set pioneered

by AMD. Without 64-bit support, the Core Duo can't easily

address more than 4GB of memory, and it loses out on

the potential performance gains offered by x86-64's

additional registers. Being stuck at under 4GB won't

matter much for the Core Duo's success in mobile applications,

and it's not likely to harm its prospects inside of

Intel's Viiv-branded home theater PCs. For really beefy

desktops, workstations, and especially servers, though,

64-bit support is becoming much more important with

time. We will have to wait for Core Duo's successor,

code-named Merom and based on Intel's next-generation

Core microarchitecture, for 64-bit capabilities in an

Intel mobile processor.

Core

Duo is part of Intel's newfangled Centrino platform,

code-named Napa. The Core Duo's main companion in the

Napa scheme is the mobile version of Intel's 945G core

logic chipset, the 945GM. The 945GM north bridge chip

is linked to Core Duo by means of a 667MHz system bus,

and the 945GM's memory controller supports dual channels

of DDR2 memory at up to 667MHz. That gives the chipset

twice the effective bandwidth of the front-side bus,

a disparity Intel has accepted as normal. In many Centrino-based

laptops, the excess bandwidth will be used to feed the

945G's integrated graphics processor, the GMA 950.

In

part because it needs this new chipset with support

for higher bus speeds, the Core Duo is not a drop-in

replacement for the Pentium M. In fact, although it

has 479 pins on its belly, the Core Duo uses a different

pin layout than the Pentium M, making it physically

incompatible with older Socket 479 motherboards

|